近日,澳大利亚新南威尔士大学(UNSW)孵化的量子初创公司Diraq,与比利时半导体研究机构IMEC联合,在《自然》发表重要成果:他们利用标准的12英寸晶圆半导体工艺制造的硅自旋量子比特单元实现了保真度超过99%的单比特与双比特量子门。这意味着,硅量子芯片不再只是实验室里的“手工艺品”,而是有望走向大规模、标准化、工业化的产品。

相关研究论文于9月24日在以“Industry-compatible silicon spin-qubit unit cells exceeding 99% fidelity(工业生产的硅自旋量子比特单元保真度超过 99%)为题发表在国际学术期刊《自然》(Nature)上。

过去实验室中制作的硅量子比特器件,虽性能优异,但一致性差、难以扩展。此次突破的关键在于,Diraq团队首次将硅自旋量子点搬上了与CMOS兼容的晶圆工艺线,并在多个器件上保持了高水平的性能。研究人员选取了四个量子比特单元,全部实现了单、双比特操作保真度超过99%,态制备与测量(SPAM)保真度更是高达99.9%;同时,器件展现出极佳的量子相干性:自旋寿命 T₁ 最长达9.5秒,Ramsey相干时间 T₂*为40.6微秒,自旋回波(Hahn Echo)下的 T₂ 接近1.9毫秒。这些指标已跨过实现量子纠错所需的关键门槛。

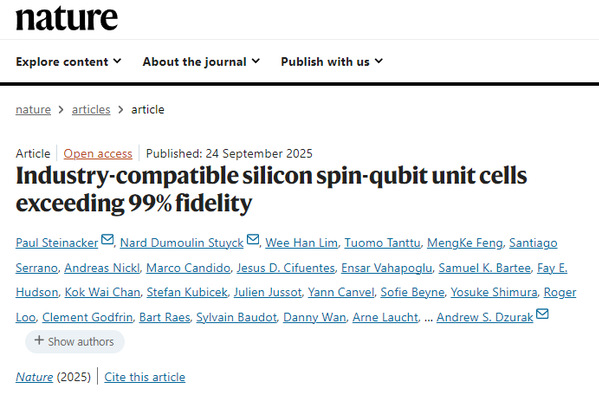

图1:a,在 300 毫米晶圆上制造的 Diraq 双量子比特器件的示意图,从下到上显示了整片晶圆、单芯片和单器件的层级结构。b,器件A的电荷稳定性图以及参数设定点:单比特门(Joff < 1 千赫兹,三角形)、双比特门(Jon ≈ 1 兆赫兹,倒三角)和读出(星形)。

这一成果背后有诸多技术亮点。材料方面,团队使用了高度同位素提纯的28Si(核自旋为0)材料,显著降低了衬底残余核自旋(29Si核自旋仅剩万分之四)的磁噪声引起的退相干。结构方面,采用三层堆叠的多晶硅栅极,栅极间距小于100纳米,并集成了单电子晶体管(SET)用于高灵敏读出,同时在芯片上布置了微波天线以实现电子自旋共振(ESR)操控。操作条件上,器件工作在约10毫开尔文的稀释制冷机中,外加约0.66–0.7特斯拉的静磁场。单比特门由精确的微波脉冲实现自旋翻转,双比特CZ门则通过J交换门调控电子间的相互作用来实现。为确保结果可靠,研究团队采用了严格的门层析(Gate Set Tomography,简写为GST) 方法对量子门进行全面表征,并分析了误差来源。结果显示,主要限制因素依然来自残余核自旋杂质,未来可通过进一步的同位素提纯优化。

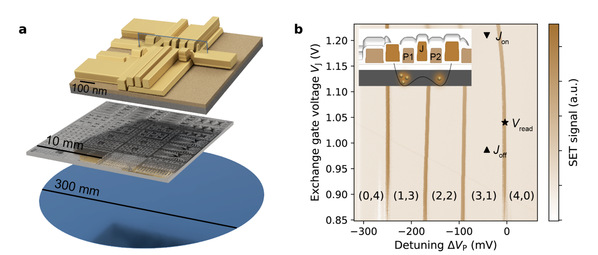

图2:比利时微电子研究中心(IMEC)生产的来自同一晶圆的16组量子点器件的栅极开关特性(EB1, P1, J, P2, EB2, RG, CBs)。在1开尔文探针台测试中均表现出非常一致的开关曲线。

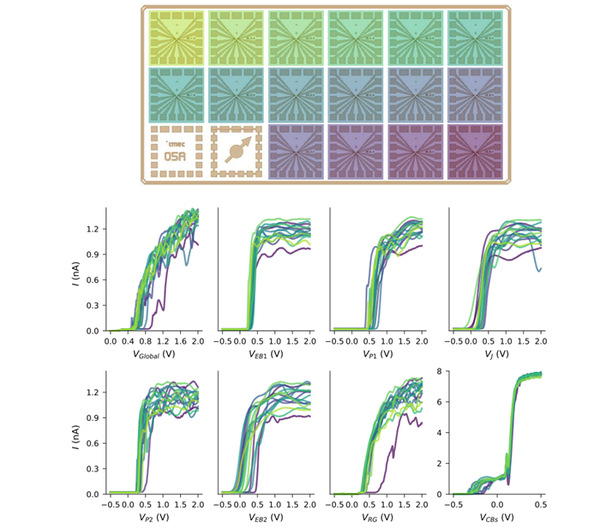

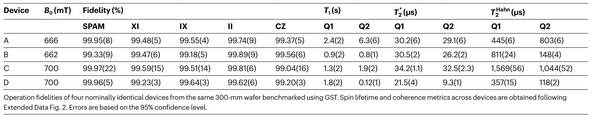

表1:器件性能的可重复性

与以往只展示单个高性能器件的实验室演示不同,本研究突出了一致性与可重复性——四个器件的性能高度接近(如表1),这表明在工业条件下生产的硅自旋量子比特芯片也能做突破容错阈值的量子操控,为硅自旋量子计算芯片的规模化奠定了基础。

然而,这项工作并不意味着硅自旋量子计算已具备应对大规模集成的挑战。目前,当前硅基量子比特规模的国际最先进水平来自UNSW的Michelle Simmons团队,在一个芯片里集成了11个量子比特,距离量子计算的第一个里程碑——“量子计算优越性”还存在较大差距。要实现大规模乃至实用化的硅基量子处理器,仍需跨越多重系统级挑战:包括材料中的残余核自旋和界面缺陷、低温驱动电子时的热功耗、成千上万布线的互连与封装、高并行度的量子态读取方案、长期运行中的自动化校准与漂移补偿,以及逻辑量子比特所需的庞大纠错开销等等。

这些技术挑战已超出单纯半导体工艺优化的范畴,必须依赖材料、控制电子、封装工程与软件等多个领域的长期协同发展。而半导体工艺的价值在于,待硅基量子计算的多比特高保真度操控和大规模集成技术实现突破后,可以较快基于半导体产线构建工业级量子计算芯片制造链。